Superskalarna arhitektura procesorjev: definicija, delovanje in prednosti

Razumite superskalarno arhitekturo procesorjev: definicija, delovanje in prednosti — paralelno izvrševanje, več enot, večja zmogljivost in učinkovitost.

Superskalarna zasnova procesorja omogoča obliko vzporednega računanja, imenovano vzporednost na ravni ukazov, znotraj enega samega procesorja. To pomeni, da procesor v enem taktu lahko izvede več kot eno navodilo tako, da hkrati pošilja navodila na več podvojenih funkcionalnih enot (ta faza se pogosto imenuje pošiljanje navodil). Vsaka funkcionalna enota je vir za izvajanje v jedru procesorja – na primer aritmetična logična enota (ALU), enota s plavajočo vejico (FPU), množilnik ali enota za vektorske/SIMD operacije.

Kako deluje superskalarni procesor

Osnovna ideja je povečati izkoriščenost strojne opreme s sočasnim izvajanjem neodvisnih navodil. Glavni koraki v izvedbi ukaza so običajno:

- pridobivanje navodil (fetch),

- dekodiranje (decode),

- dispečiranje/pošiljanje navodil na razpoložljive funkcionalne enote (issue/dispatch),

- izvajanje (execute),

- zapis rezultata (writeback) in

- potrditev oziroma umik (commit/retire).

Dispečer navodil prebere na voljo verigo ali okno navodil iz pomnilnika in odloči, katera navodila se lahko izvajajo vzporedno glede na njihove medsebojne odvisnosti. Ključne funkcije, ki to omogočajo, so:

- Navodila so organizirana v urejenem seznamu oziroma oknu navodil.

- Strojna oprema lahko ugotovi, katera navodila so odvisna od podatkov (data hazards) in katera so neodvisna.

- Procesor lahko prebere več navodil v enem taktovnem ciklu in jih izda na več enot hkrati.

Ključne komponente in tehnike

- Večizhodne/fazne funkcionalne enote: več ALU, FPU in SIMD enot omogoča sočasno izvajanje aritmetike, plavajoče vejice in vektorskih operacij.

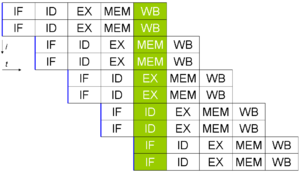

- Cevovodno (pipeline) vezje: večina superskalarnih procesorjev uporablja cevovodno izvedbo za razdelitev izvajanja ukazov v več stopenj, kar povečuje prepustnost.

- Dinamično razporejanje: tehnike, kot so rezervacijske enote (reservation stations), reorder buffer in register renaming, omogočajo izvajanje navodil izven vrstnega reda (out-of-order), hkrati pa zagotavljajo pravilno semantiko programa ob končni potrditvi (in-order commit).

- Napovedovanje vejitev (branch prediction): kompleksni mehanizmi za napovedovanje skokov zmanjšujejo vpliv kontrolnih hazardov in povečujejo možnost, da so funkcionalne enote dejansko zasedene.

- Širše okno navodil (instruction window): večje okno pomeni več priložnosti, da dispečer najde neodvisna navodila za izvajanje.

Razmerje med skalarnim, vektorskim in superskalarnim

Vsak ukaz, ki ga izvede skalarni procesor, običajno spremeni en ali dva podatkovna elementa, medtem ko vektorski (ali SIMD) ukazi obdelajo več podatkovnih elementov s enim ukazom. Superskalarni procesor je nekakšna mešanica: vsak posamezen ukaz običajno deluje na en podatkovni element, vendar ima jedro več podvojenih funkcionalnih enot, tako da lahko sočasno obdela več neodvisnih ukazov nad različnimi podatkovnimi elementi.

Prednosti

- Večja prepustnost (throughput): izvedba več ukazov na takt poveča skupno zmogljivost.

- Boljša izraba strojne opreme: razpršitev dela po več enotah zmanjša čas, ko so posamezne enote neaktivne.

- Povečanje IPC (instructions per cycle) brez nujne povečave takta.

- Združljivost z obstoječimi programskimi modeli – izboljšave so predvsem v strojni opremi, programi pogosto delujejo hitreje brez sprememb.

Omejitve in izzivi

- Omejena navidezna vzporednost (ILP): ne glede na število enot je razpoložljiva vzporednost omejena z odvisnostmi v programu.

- Kompleksnost strojne opreme: dinamično razporejanje, register renaming in močnejše napovedovalnike povečajo logiko, porabo površine (area) in porabo energije (power).

- Strukturni konflikti: če dispečer ne more zasedeti vseh enot (na primer zaradi pomanjkanja virov ali odvisnosti), zmogljivost ne doseže maksimalne teoretične vrednosti.

- Povratne lawine vračanja (rollback) pri napovedovanju vejitev: napačne napovedi pomenijo razveljavitev dela in izgubo ciklov.

- Zaključni stroški za skalabilnost: z naraščanjem števila izvajalnih enot se povečuje zapletenost koherentnosti, dostopa do registre in nadzora odvisnosti.

Razlike in primerjava s sorodnimi tehnikami

- Superskalarno vs. VLIW: pri VLIW (Very Long Instruction Word) kompilator skompilira več neodvisnih operacij v eno daljšo besedo in tako odloča o vzporednosti, medtem ko superskalarni procesor dinamično ugotavlja vzporednost v strojni opremi.

- Superskalarno vs. SMT (Simultaneous Multithreading): superskalarni procesor povečuje paralelizem na ravni ukazov z znotraj-jedrskimi več enotami; SMT omogoča več niti, da delita iste izvršilne enote in s tem izboljšajo izkoriščenost, še posebej ko posamezna nit nima dovolj ILP.

Zgodovina in primeri

Koncept superskalarnega izvajanja se je razvil v 1970-ih in 1980-ih. V praksi so v sodobnih potrošniških in strežniških procesorjih superskalarne zasnove postale standard; izdelovalci običajno kombinirajo več ALU, FPU in SIMD enot za združevanje prednosti različnih vrst izvajanja. Tipična sodobna jedra pogosto vključujejo več ALU-jev, večenotno plavajoče vejice in specializirane SIMD enote, pri čemer natančne konfiguracije variirajo glede na arhitekturo in namen procesorja.

Načrtovanje in optimizacija

Pri načrtovanju superskalarnih procesorjev je cilj povečati skladnost in zanesljivost izvrševanja ter maksimirati izrabo funkcionalnih enot. To vključuje uravnoteženje med velikostjo okna navodil, kompleksnostjo razporejevalnikov, učinkovitostjo napovedovalnikov vejitev in stroški (poraba energije, površina čipa). Kompilatorji lahko pomagajo z reorganizacijo kode (statistična optimizacija), vendar je večina sodobnih superskalarnih izboljšav vgrajena v strojno opremo procesorja.

Sinteza

Superskalarna arhitektura povečuje zmogljivost procesorjev z izvajanjem več nepovezanih navodil hkrati znotraj jedra. Dosežejo jo z razporejanjem navodil v več funkcionalnih enotah, dinamičnim upravljanjem odvisnosti in naprednimi tehnikami, kot so register renaming in napovedovanje vejitev. Čeprav prinaša pomembne prednosti v hitrosti in izkoristku virov, se srečuje tudi z omejitvami, ki izhajajo iz kompleksnosti, porabe energije in naravnih omejitev navidezne vzporednosti v programih.

Za nadaljnje branje o povezanih temah si lahko ogledate viri o arhitekturi procesorjev, naprimer o konceptih cevovodnega vezja, dinamičnem izvrševanju in naprednih mehanizmih napovedovanja vejitev.

Procesorska plošča vzporednega računalnika CRAY T3e s štirimi superskalarnimi procesorji Alpha

Enostaven superskalarni cevovod. S pridobivanjem in pošiljanjem dveh navodil hkrati je mogoče dokončati največ dve navodili na cikel.

Omejitve

Izboljšanje zmogljivosti pri zasnovi superskalarnih procesorjev je omejeno z dvema dejavnikoma:

- Stopnja vgrajenega vzporedništva na seznamu ukazov

- zapletenost in časovni stroški dispečerja in preverjanja odvisnosti podatkov.

Tudi ob neskončno hitrem preverjanju odvisnosti v običajnem superskalarnem procesorju, če ima sam seznam ukazov veliko odvisnosti, bi to prav tako omejilo možno izboljšanje zmogljivosti, zato je dodatna omejitev količina vgrajenega paralelizma v kodi.

Ne glede na hitrost dispečerja obstaja praktična omejitev, koliko navodil je mogoče hkrati poslati. Medtem ko bo napredek strojne opreme omogočil več funkcionalnih enot (npr. ALU) na jedro procesorja, se problem preverjanja odvisnosti ukazov poveča do te mere, da je dosegljiva meja superskalarnega dispečiranja nekoliko manjša. -- Verjetno gre za pet do šest istočasno poslanih ukazov.

Alternative

- Hkratno večnitno branje: pogosto skrajšano kot SMT, je tehnika za izboljšanje splošne hitrosti superskalarnih procesorjev. SMT omogoča več neodvisnih niti izvajanja, da se bolje izkoristijo viri, ki so na voljo v sodobnem superskalarnem procesorju.

- Večjedrni procesorji: superskalarni procesorji se od večjedrnih razlikujejo po tem, da več redundantnih funkcionalnih enot ni celotnih procesorjev. En sam superskalarni procesor je sestavljen iz naprednih funkcionalnih enot, kot so ALU, množilnik celih števil, prestavljalnik celih števil, enota s plavajočo vejico (FPU) itd. Vsaka funkcionalna enota ima lahko več različic, kar omogoča vzporedno izvajanje številnih ukazov. To se razlikuje od večjedrnih procesorjev, ki sočasno obdelujejo navodila iz več niti, po eno nit na jedro.

- Procesorji s cevnimi povezavami: superskalarni procesorji se razlikujejo tudi od procesorjev s cevnimi povezavami, kjer je lahko več ukazov hkrati v različnih fazah izvajanja.

Različne alternativne tehnike se med seboj ne izključujejo - v enem procesorju jih je mogoče kombinirati (in jih pogosto tudi kombiniramo), zato je mogoče zasnovati večjedrni procesor, v katerem je vsako jedro neodvisen procesor z več vzporednimi superskalarnimi cevovodi. Nekateri večjedrni procesorji vključujejo tudi vektorsko zmogljivost.

Sorodne strani

- Vzporedno računalništvo

- Vzporednost na ravni ukazov

- Hkratno večnitno branje (SMT)

- Večjedrni procesorji

Vprašanja in odgovori

V: Kaj je superskalarna tehnologija?

O: Superskalarna tehnologija je oblika osnovnega vzporednega računalništva, ki omogoča obdelavo več kot enega ukaza v vsakem taktu z uporabo več izvajalnih enot hkrati.

V: Kako deluje superskalarna tehnologija?

O: Superskalarna tehnologija vključuje navodila, ki prihajajo v procesor po vrstnem redu, med izvajanjem išče podatkovne odvisnosti in v vsakem taktu naloži več kot eno navodilo.

V: Kakšna je razlika med skalarnimi in vektorskimi procesorji?

O: Pri skalarnem procesorju navodila običajno delajo z enim ali dvema podatkovnima elementoma naenkrat, medtem ko pri vektorskem procesorju navodila običajno delajo z več podatkovnimi elementi naenkrat. Superskalarni procesor je mešanica obeh, saj vsako navodilo obdeluje en podatkovni element, vendar se hkrati izvaja več navodil, zato procesor obdeluje več podatkovnih elementov hkrati.

V: Kakšno vlogo ima natančen dispečer navodil v superskalarnem procesorju?

O: Natančen dispečer navodil je zelo pomemben za superskalarni procesor, saj zagotavlja, da so izvajalne enote vedno zasedene z delom, ki bo verjetno potrebno. Če dispečer navodil ni natančen, bo morda treba nekaj dela zavreči, zaradi česar procesor ne bo hitrejši od skalarnega procesorja.

V: V katerem letu so vsi običajni procesorji postali superskalarni?

O: Vsi običajni procesorji so postali superskalarni leta 2008.

V: Koliko enot ALU, FPU in enot SIMD je lahko v običajnem procesorju?

O: V običajnem procesorju so lahko do 4 enote ALU, 2 enoti FPU in 2 enoti SIMD.

Iskati